发布背景

近日,姚期智院士代表标准牵头单位(交叉信息核心技术研究院)与标准起草单位(中国Chiplet产业联盟),与国内主机厂、一级供应商代表一起,发布世界首个车规级Chiplet接口标准:《车规级芯粒互连标准ACC_RV 1.0》- Road vehicles- Advanced Cost-driven Chiplet Interface(ACC_RV)(标准可通过http://accchiplet.iiisct.com/进行下载)。

近年来,新能源及人工智能产业的快速发展正在推动汽车产业的数字化变革,“新四化”大趋势下,传统分布式的汽车电子电气架构正在逐步向域控制式以及中央计算平台演进,不同类型智能座舱、智能驾驶解决方案在新车型上的创新及搭载率快速提升。汽车智能化率在高速增长的同时,也展现出产品层次及功能需求显著多元化的特点,而汽车芯片作为核心“大脑”,在传统SoC设计思路下,单芯片如何能够灵活适配于不同车型的需求,亦往往成为取舍痛点。

Chiplet架构通过将SoC中的通用模块与专用模块解耦并分别生产成小芯粒,由主机厂以及Tier1根据自身车型适配需求进行灵活选择并异构集成,可提供兼顾高性能、安全稳定、成本可控、扩展性强、迭代周期短等综合需求的解决方案,将成为未来中央计算平台硬件架构的重要的发展方向。

标准订立原则

满足最高级别功能安全(最高可支持到Asil-D级)

信号通路安全(国密算法)

针对信道优化(车规芯片与封装覆铜更厚,以增加加速度耐受力),增强高速串口均衡能力

在满足车规级功能安全、信号通路安全等的前提下,尽可能压低车规所带来的更多的Chiplet测试成本

ACC_RV 1.0车规标准总概

工作温度:支持-40~150℃。

存储保护:在存储加入ECC校验保护,实现1bit纠错,2bit以上检测出错误。

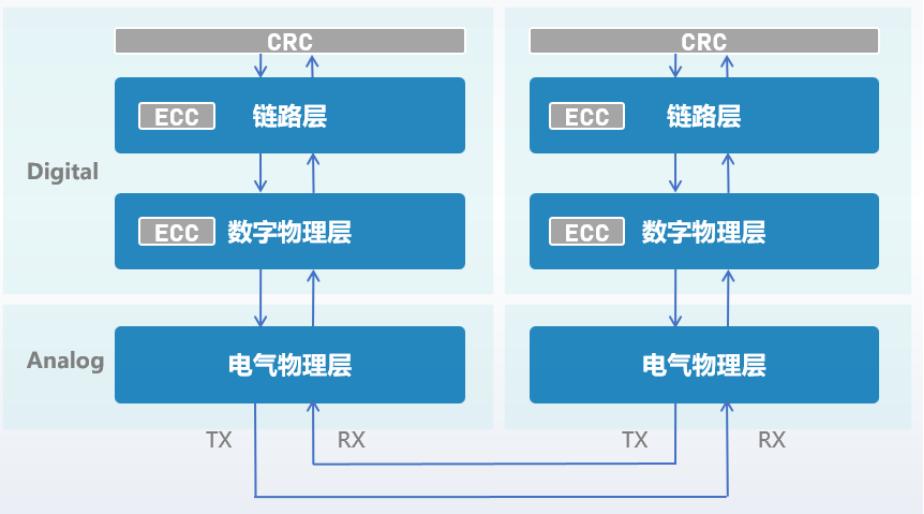

端到端总线保护:在数据输入本端链路层之前,通过CRC计算生成冗余位,当数据传输到对端链路层后,进行CRC校验,从而避免数据在传输过程中的失效问题。

芯片监控:加入电压、温度的监测逻辑,支持上报。

启动自检:在芯片上电的时候进行逻辑自检。在关机下电时,完成逻辑自检,并将自检结果留存,待下次上电时读取。自检若出错,则直接上报。支持安全岛主动发起自检。

冗余信道:在信道组之外,需要添加冗余信道。当某一信道发生故障时,支持用冗余信道去替换故障信道。

快速测试:信道设计上加入一个旁路模式,即复用信道。这个模式复用Chiplet高速串口为测试通道输入端口,测试激励通过测试通道输入端口,进入片内进行测试;同时,Chiplet高速串口可以被复用为测试通道输出端口,片内响应通过测试通道输出端口,输出片外观测。由于高速串口的高速度,可以极大加快测试速度,减少机台占用时间。

信道的Loopback测试:Loopback测试能够满足,封装之前信道通路的自检自测,可提前发现故障,加快测试速度。

1.存储器自测试及修复(MBIST and Memory repair)

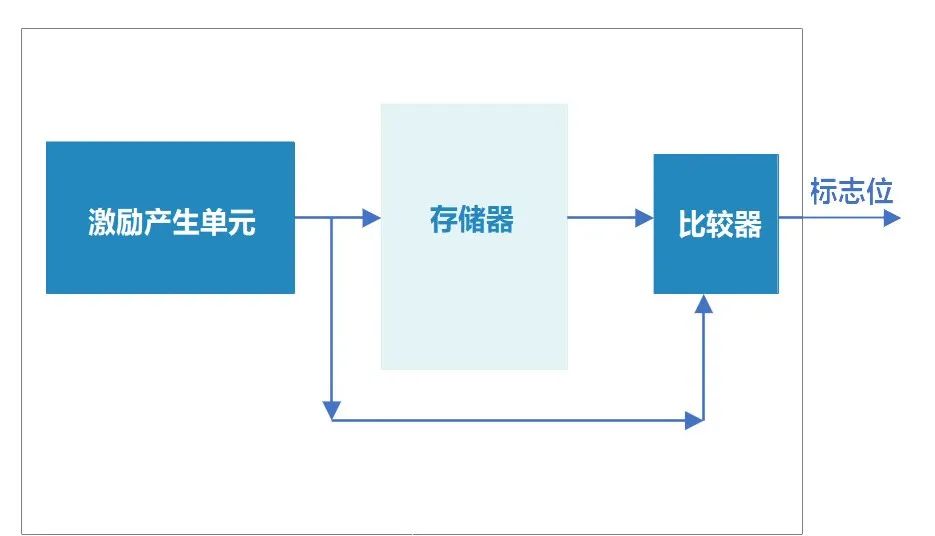

对嵌入式存储器需要采用内建自测试结构,目标是在车辆使用场景下,随时能够启动测试,并且使用尽可能少的测试管脚,来完成控制激励输入,检测输出。存储器自测试结构需要内置激励产生单元,在启动测试信号拉高后产生测试激励对存储器进行读写操作,读取存储器内部值,在比较器内与期望值进行对比。对比结果通过一个标志位输出,通过标志位信号可以判断存储器是否存在缺陷。

上述对存储器的读写操作,即对连续地址空间升序或降序写入特定数值,并读出,这种读写操作称为测试算法。复杂算法带来更高的覆盖率,保障功能安全。

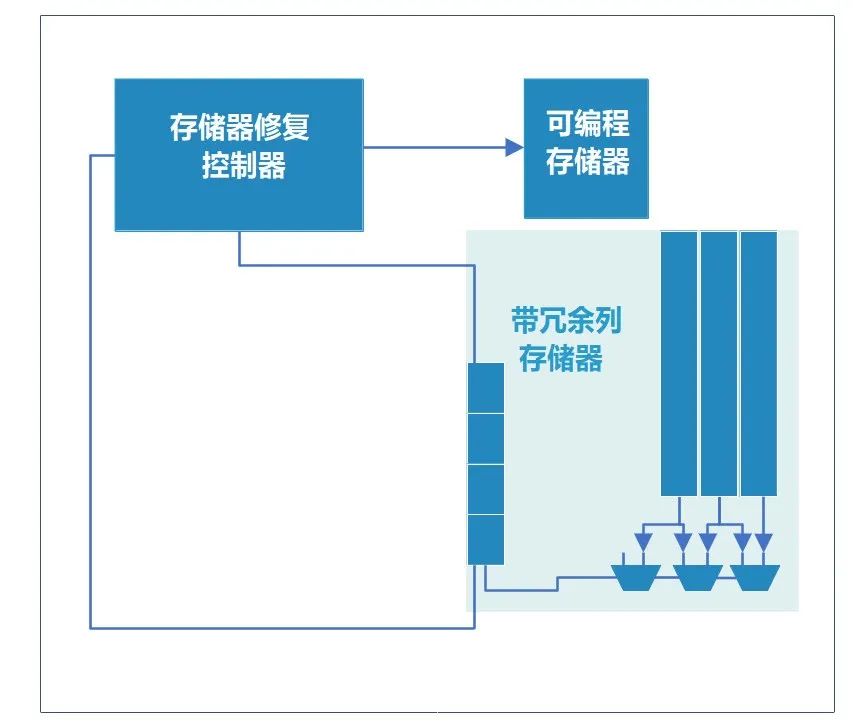

为了满足车规功能安全需求,存储器测试需要包含自修复功能。测试方案包括,必须选择带有冗余行/列逻辑的存储器,当存储器自测试发现存储器故障时,用冗余行/列替换故障行/列,并将这种替换信息存入片上可编程存储器。

存储器自测试与修复,很大程度上提高了芯片良率和可靠性,增强后期使用中发生故障时的处理能力,适用车规应用场景。

2.逻辑自测试(LBIST)

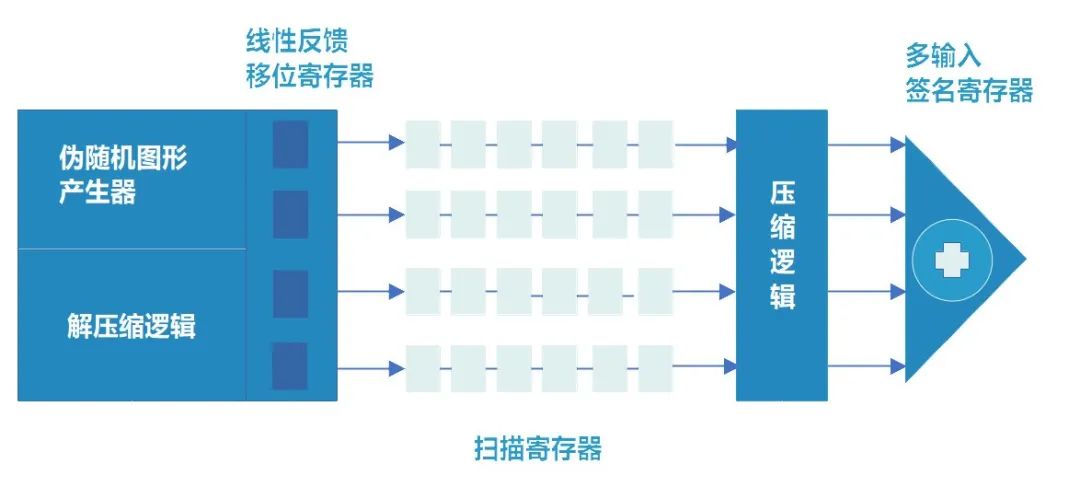

车规使用场景下,芯片需要满足自测试。所以对于片上逻辑需要加入自测试结构;同时考虑顶层管脚资源的限制,使用压缩逻辑,将数目庞大的测试扫描链,压缩为若干个测试通道;扫描链的输出经过压缩逻辑,压缩成若干输出。

逻辑自测试启动后,伪随机图形产生器产生测试图形,经过内置有线性反馈移位寄存器的解压缩逻辑解压后灌入扫描链中,通过一系列移位,捕获,再移位操作,抓取电路反馈值并且与期望值相比,判断电路是否存在故障。额外的,需要一个压缩逻辑对多扫描链的输出进行压缩后,再次进入一个多输入签名寄存器电路,在这里和期望值进行对比,大大减少了管脚数目。

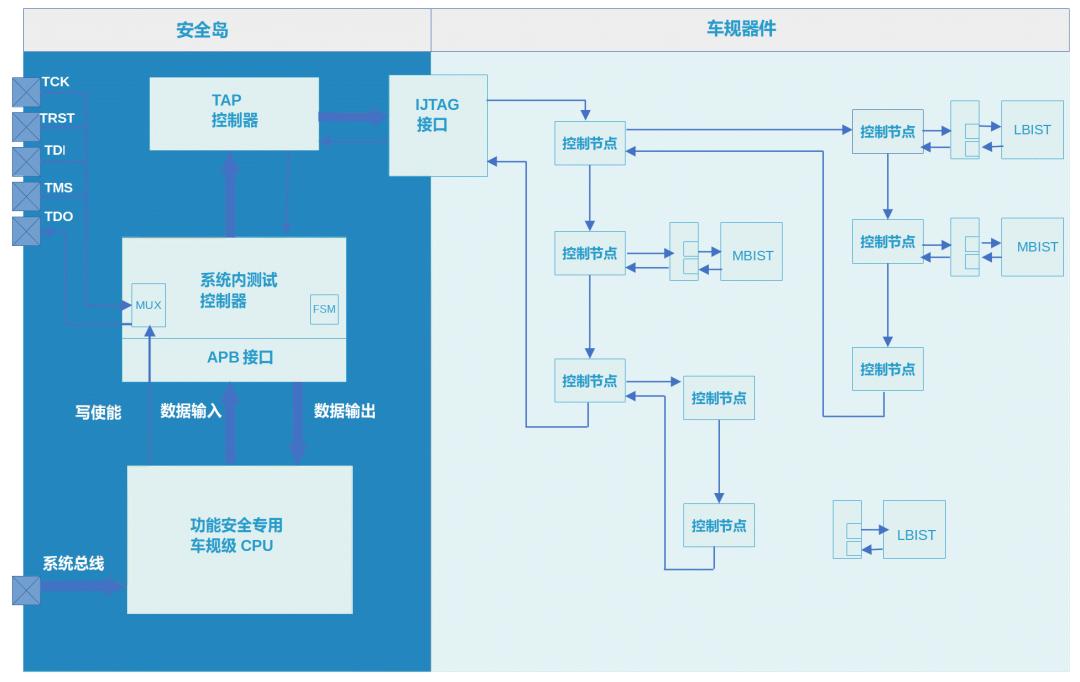

3.安全岛控制

自测试必须受到来自安全岛的专用车规CPU的控制,在车辆上电或空闲时,启动测试。测试时,专用车规CPU发送测试指令,通过总线接口,对系统内测试控制器进行操作,最终由系统内测试控制器通过标准测试访问接口启动测试,收集结果。安全岛内CPU采用双锁步设计,为测试程序安全运行提供保障。

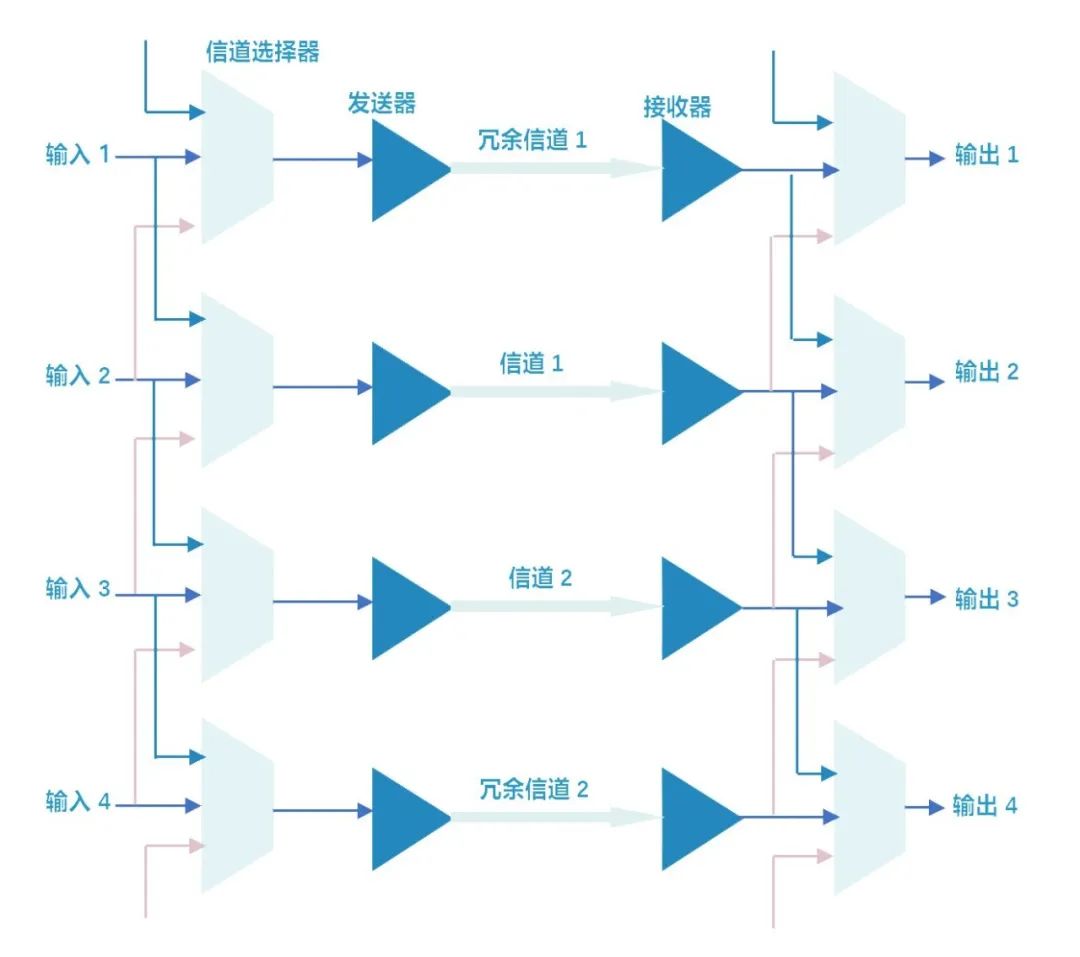

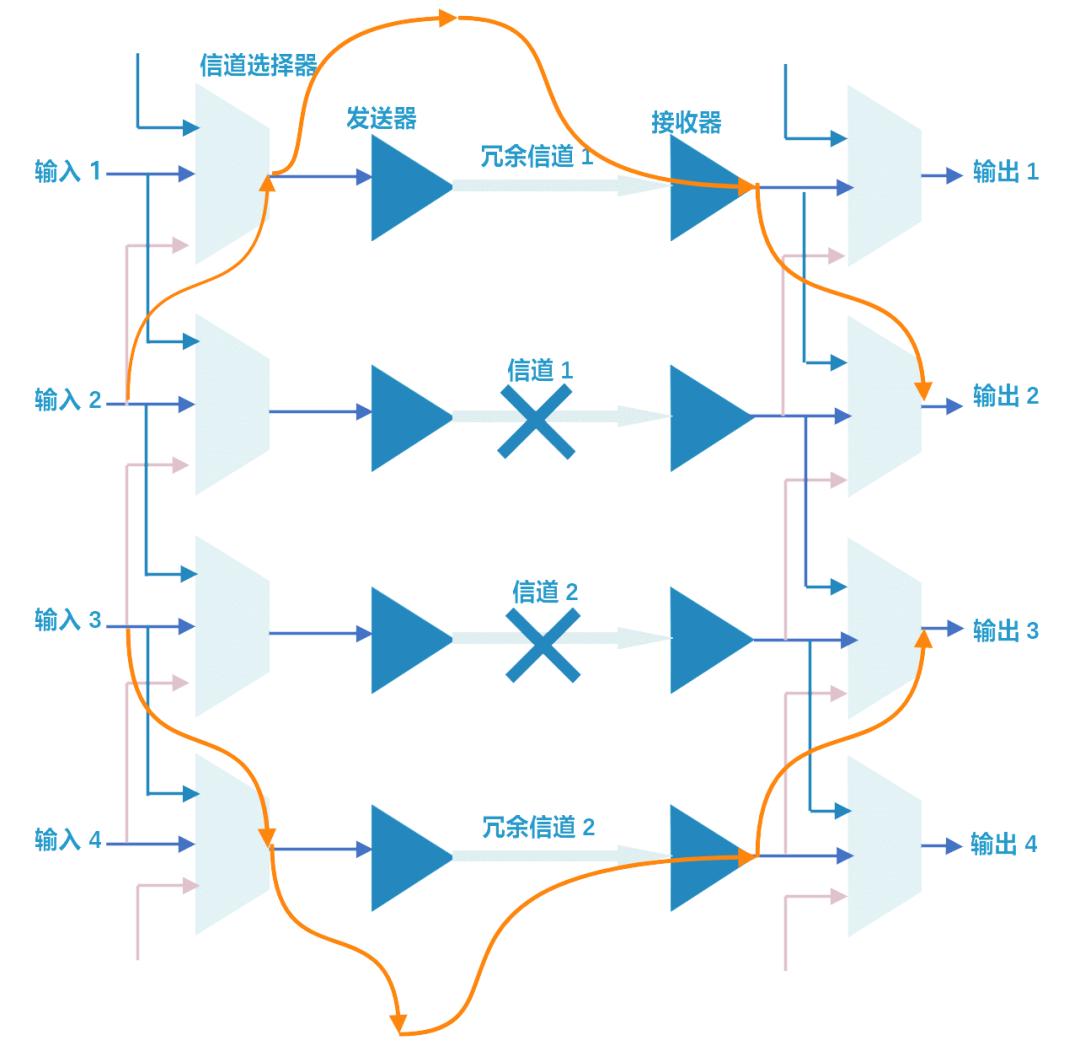

4.信道冗余及重映射设计

在信道组之外,需要添加冗余信道。当某一信道发生故障时,用冗余信道去替换故障信道,这一冗余设计将提升良率和可靠性。

在信道的发送端,接收端分别加入一个3输入的信道选择器,信道的信号逐次送入相邻两边信道选择器,这样,如果信道1发生故障,通过控制选择器的选择端,将输入2映射到冗余信道1的选择器上,通过冗余信道的发送器发送输入2,同时冗余信道1的接收器输出,再映射回到原先信道1的输出2,这样输入2到输出2的传输就通过冗余信道1完成。同理,信道2故障时,输入3到输出3的传输,可以向下映射到冗余信道2上进行。

这种冗余设计大大提高了可靠性,使用与车规测试后的修复。由于车规测试的复杂性,标准中特加入快速测试相关模式,具体方法如下:

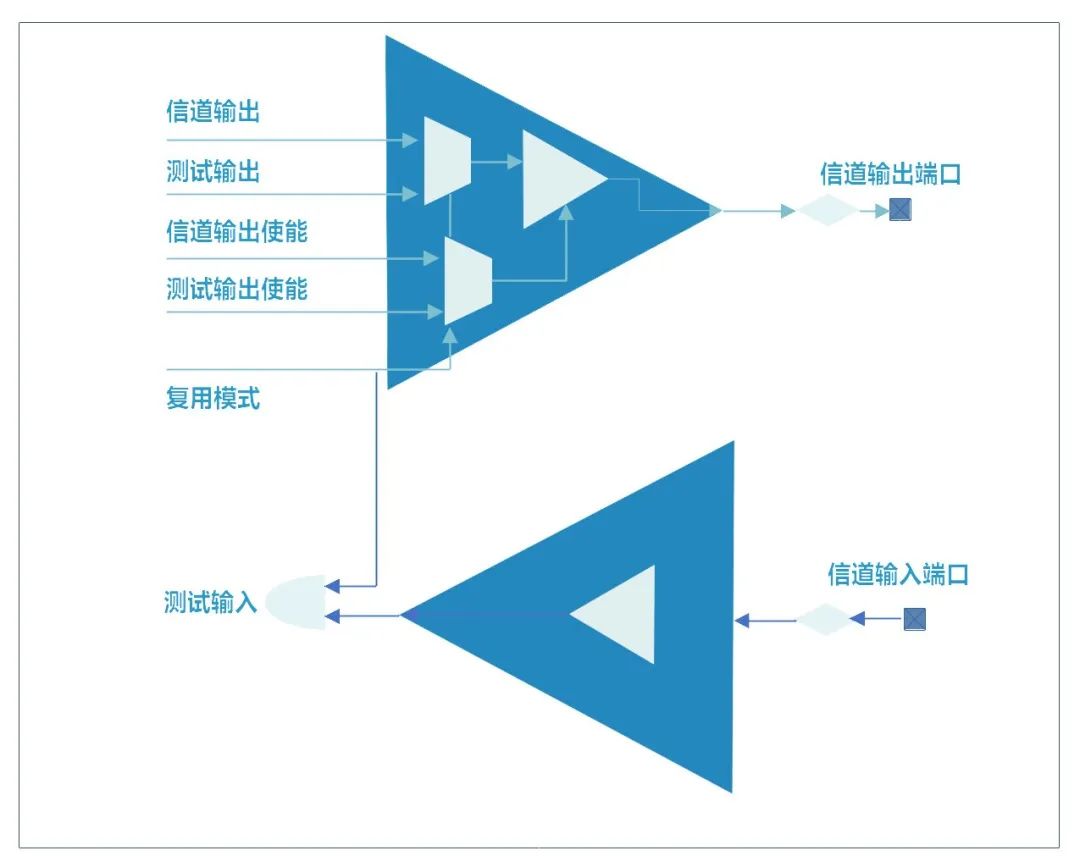

1.信道旁路模式

信道设计上加入一个旁路模式,即复用信道。这个模式使差分输入端口可以被复用为测试通道输入端口,测试激励通过测试通道输入端口,进入片内进行测试;同时,差分输出端口可以被复用为测试通道输出端口,片内响应通过测试通道输出端口,输出片外观测。高速差分端口的复用为测试通道端口,可以加快测试速度。

旁路模式规定,差分信道输入可以直接被导入片内,输入信道被旁路;差分信道输出可以直接来自片内,输出信道被旁路。

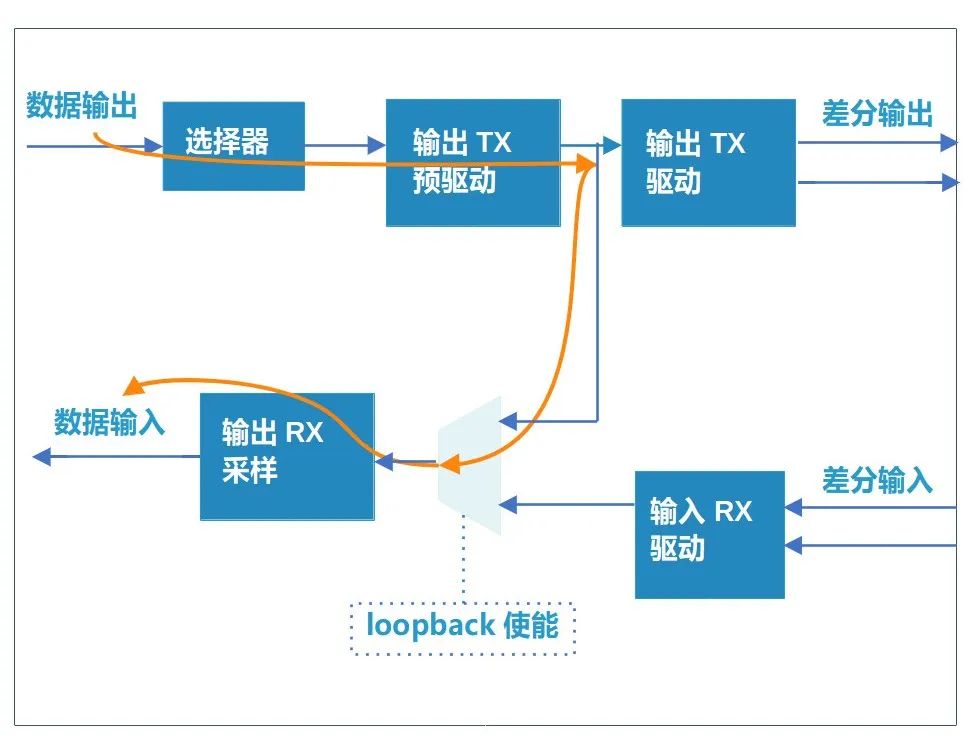

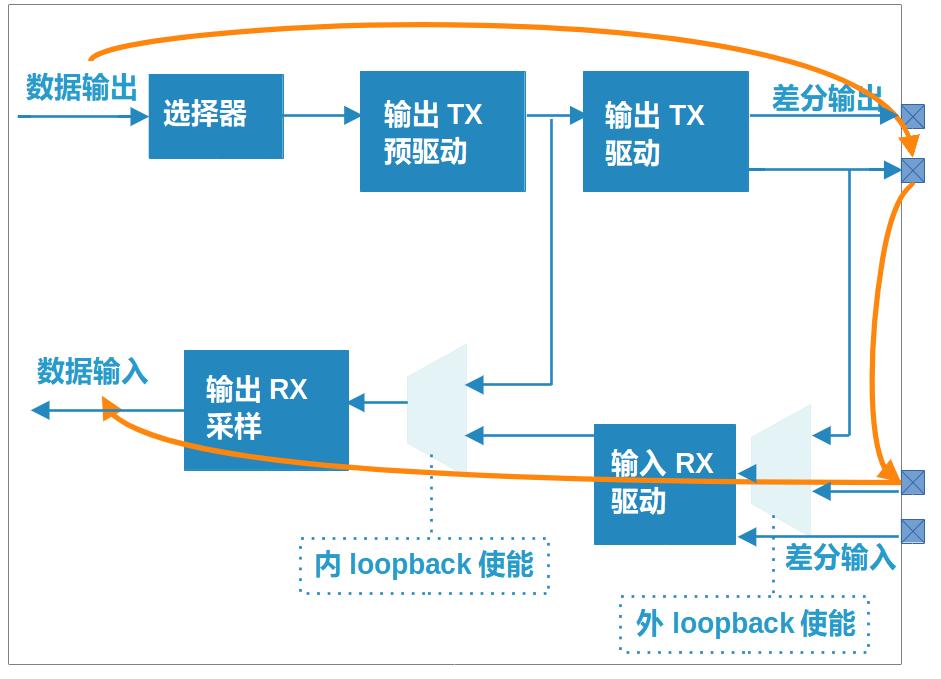

2.信道的Loopback测试

内loopback模式中,输出侧输出预置测试图形,通过内部选择环回到输入侧,输入测采样数据和预置测试图形进行对比,判断内部信道通路是否正常。

外loopback模式中,输出侧输出预置测试图形,必须通过输出端口输出到片外,并且通过输入侧的选择器环回到输入侧,输入测采样数据和预置测试图形进行对比,判断内部信道通路是否正常。

Loopback测试能够满足,封装之前信道通路的自检自测,可提前发现故障,加快测试速度。

ACC_RV同期通过开放原子基金会“元遨”开源智能出行项目发布。