近日,清华大学姚期智院士代表中国Chiplet产业联盟,联合国内外IP厂商、国内领先封装厂商、国内领先系统与应用厂商共同发布了《芯粒互联接口标准》- Advanced Cost-driven Chiplet Interface(ACC),该标准由交叉信息核心技术研究院牵头,中国Chiplet产业联盟共同起草。目前该标准涉及相关的团体标准、行业标准在申请中。

标准发布背景

随着摩尔定律逐渐逼近物理及商业极限,基于Chiplet的芯片设计理念逐渐成为后摩尔时代行业发展趋势。2020年9月,在西安硬科技大会上,中国Chiplet产业联盟(China ChipLet League (CCLL))启动成立,旨在于以国家产业政策为导向,以市场为驱动,以企业为主体,搭建产业生态合作平台,共同制定Chiplet 互联标准,共建 Chiplet 技术开放平台,构建我国蓬勃发展的 Chiplet 产业生态。

国内的半导体产业尚处于发展期,尤其在当今国际形势下亦将长期处于追赶阶段,产业链各环节上与国际领先技术水平相比仍有一定差距。在晶圆制造环节:受各方面因素限制,国内晶圆厂短期内难以实现14nm及以下先进工艺节点的大规模量产,尤其在高性能计算领域所需的大面积芯片整体良率仍处于较低水平,当前趋势下甚至需考虑通过工艺回撤实现成本可控的商业路径。在封装测试环节:国内传统封装技术相对成熟,在2.5D先进封装技术等方面亦取得了一定成果,但作为关键材料的ABF基板尚需依赖海外供应链,国内基板层数方面相对落后,在系统级较为重视的连接密度、线宽线距、通孔过孔盲孔工艺和毛刺控制方面与一线国际水平相比还有差距。

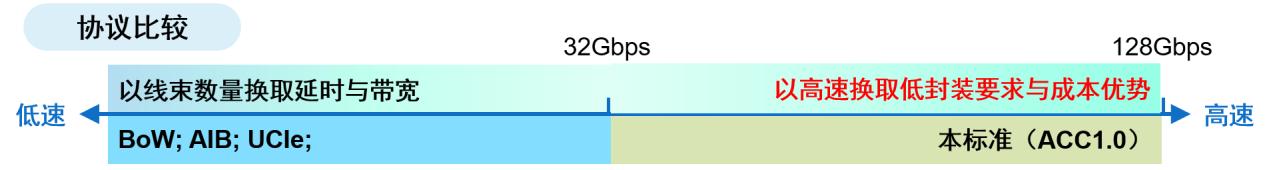

在上述产业背景下,国内Chiplet产业化亦面临诸多落地困难:如在接口方面:目前国内研发重点主要集中在低速接口标准(如UCIe),时延性能较好但对先进封装及载板等要求较高,且封装成本较高,商业化存在难度;而高速接口核心技术把握在海外IP厂商,在国内亦缺乏有效需求和产品定义。在芯粒产品方面:目前国内芯粒产品较为有限,尽管有众多企业已在IP芯粒化、接口芯粒化等方面加大投入并逐步产品化,但由于Chiplet缺乏标准化测试及集成流程,而下游产业各场景方的需求又较为多元化,目前尚未形成商业可行的Chiplet产品方向。

我们认为,当前形势及环境下,国内半导体产业在Chiplet上要有所突破,所面临的挑战和机遇在于:如何在现有相对落后的制造工艺、尚在发展中的先进封装技术以及相关核心材料供应链的基础上,做出满足性能预期且成本可控的产品,使得Chiplet真正具有商业可行性。而在此背景下,中国Chiplet产业的发展需要上下游共同建立产业生态,以下游需求带动上游资源投入,以量产的规模经济换取成本优势,最终形成良性发展循环。

基于上述目标,并立足于国内供应链成熟程度的现状,中国Chiplet产业联盟联合国内系统、IP、封装厂商一起,制定了《芯粒互联接口标准》ACC1.0,该标准为高速串口标准,着重基于国内封装及基板供应链进行优化,以成本可控及商业合理性为核心导向。目前该标准涉及相关的团体标准、行业标准在申请中。

与国际相关标准的融合

2022年Intel、AMD、台积电等全球十大相关企业巨头成立了UCIe联盟,提供了高至32G带宽的芯粒互联标准,适用于2.5D以及3D先进封装(如Intel EMIB、台积电CoWoS等等)。而中国Chiplet产业联盟本次发布的《芯粒互联接口标准》ACC为32G以上带宽的高速串口标准,侧重于针对国产基板及封装供应链体系的优化和适用性,以及成本可控。

两者的适用性区别主要在于面向的行业领域以及最终用户场景可接受的成本结构:在追求超高性能计算的领域,尽管UCIe所需采用的先进封装量产成本可能占到芯片总成本的60%~70%甚至更高,但以小面积芯粒互联的方式可有效解决先进工艺制程下大面积芯片良率痛点,在出货量较大的情况下具有较高的商业价值。而在成本较为敏感、出货量规模有限、供应链能力偏弱、保供要求较高的诸多下游领域,采用ACC标准更加能够满足商业可行性的需求。

总体而言,中国Chiplet产业链以及最终Chiplet产品必须要融合并参与到全球竞争,因此在标准适用性方面还应当海纳百川,允许标准间相互竞争、兼容、融合。目前由于UCIe并未定义32GHz以上频点的标准,ACC也并未定义32GHz以下频点的标准,两者实现在32GHz频点上的兼容。

ACC标准适用场景

从技术层面,ACC标准作为高速串口标准,适用于固定的、可提前预知的数据流结构多Die封装。若可提前预知数据流结构,便可以提前进行数据搬运。数据对带宽敏感,对延迟敏感的要求,可通过数据预读取、编译进行优化。

如上所述,从应用领域来看,ACC标准更加适用于各类异构计算场景,如各类AI加速产品、GPU、FPGA、多核CPU Die内已经互联后与其他异构模块交互等。对多个单核CPU互联中数据流不可预知的Coherence交互场景,ACC标准的延迟对整体性能影响较大。

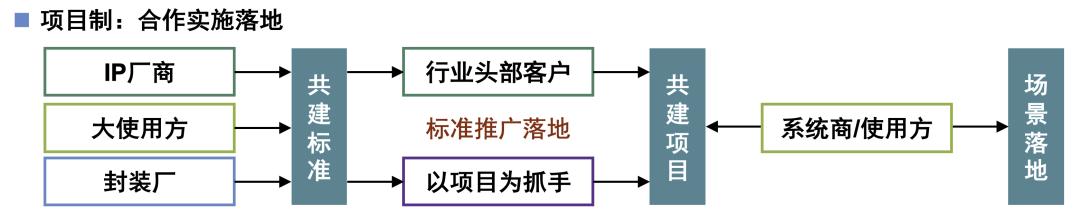

产业生态构建及商业化路径

当前国内外主流半导体巨头均有根据自身产品需求所采用的内部互联标准,但均未对外授权开放使用,中国Chiplet产业联盟发布的ACC标准就是要顺应行业发展潮流,以商业落地为主要目标,通过差异化的技术优势以及极具吸引力的授权价格,最终取得市场广泛使用及推广。

有别于UCIe基于全球供应链及先进封装,ACC标准基于国产基板及封装能力在接口层面进行优化,并且以成本可控作为主要切入点。ACC标准在联盟内部已经推动了相关企业进行研发,相关企业近期将陆续推出基于ACC标准的相应接口产品,并以此推动基于Chiplet的异构集成相关方案,以解决国内大算力需求SoC市场普遍存在的开发周期长、风险大、迭代慢、投入大等痛点。

在此共建标准的基础上,行业内各半导体设计公司可联合行业头部客户群,以项目为抓手,进一步共建项目以丰富Chiplet芯粒库,推动Chiplet方案在各商业场景应用,从而真正实现国产Chiplet方案的加速落地。

标准细节

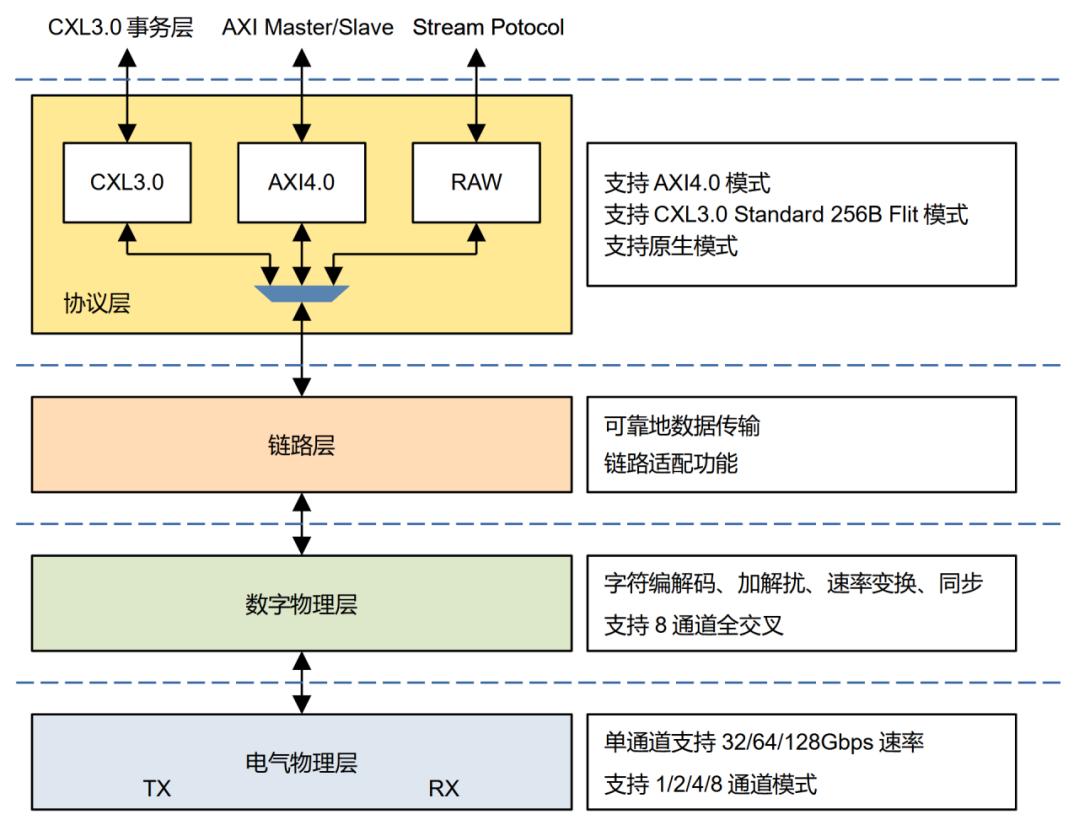

标准定义思路:

严控成本为第一优化目标,采用高速Serdes为接口,提高单线性能以拉平接口损耗

超低误码率,采用出错重传机制,而非FEC纠错模块,以减少端口延迟

全国产工艺封装提取参数,针对MicroBump间距、线宽线距、打孔毛刺情况等针对性优化

以关键领域的实际项目为抓手,接口上耦合系统、下耦合封装进行联合优化

标准技术特点:

高速率:PHY支持8Lane*32-128Gbps传输率,Controller支持8Lane*32/64/128Gbps

低延迟:端到端延迟<50ns(DieA的AXI总线到DieB的AXI总线延迟)

低误码:误码率小于10的负15次方

高可靠:IP控制器的链路层,支持CRC和出错重传,满足无差错传输需求

兼容广:IP和系统的接口(协议层)当前支持AXI4。同时支持协议层用户自定制,用户可以开发自己的协议层,以对接不同的需求(例如对于Virtual Channel的支持)。

易使用:控制器采用采用状态机设计,自动完成建链初始化工作,仅需软件配置启动建链使能

可测试:支持3种环回模式,支持Die内环回和Die间环回测试

可配置:可通过SPI接口,对IP内部的寄存器进行配置

低成本:支持2D和2.5D封装。对国产基板情况做了针对性优化,成本更低,产能更充足稳定

DFT:内置DFT逻辑,预留DFT接口

面积小:14/12nm工艺下,8通道接口面积为2.13平方毫米

管脚少:采用高速串行SerDes传输,Signal Pad数量为32(差分数据传输)+6=38个,对规模小的die更加友好

考虑基板层数少的情况下布线难度,支持收发端通道不对齐,甚至多通道全交叉

自带眼图分析工具,考虑到高速高采样频率的信号分析仪(示波器)国际管制禁运,自带眼图打印功能