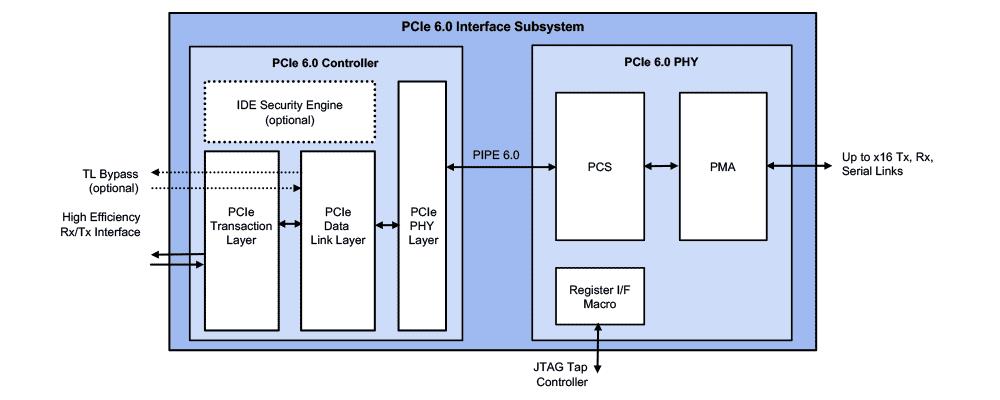

Rambus 刚刚发布了新一代 PCIe 6.0 接口子系统,旨在为下一代高性能数据中心和 AI SoC 解决方案提供鼎力支持。作为一家业内领先的芯片与硅 IP 供应商,Rambus 致力于让数据更快、更安全。而今日隆重推出的 PCIe Express 6.0 PHY 和控制器 IP,还包含了对最新的 CXL 3.0 连接规范的支持。

(来自:Rambus Press Releases)

Rambus 接口 IP 总经理 Scott Houghton 表示:

人工智能(AI)/ 机器学习(ML)和数据密集型工作负载的快速发展,正在推动数据中心架构的持续发展,同时也对性能水平提出了更高的要求。

Rambus PCIe 6.0 接口子系统可满足下一代数据中心所需的性能要求,且具有一流的延迟、功耗、面积和安全性。

规格方面,Rambus PCIe 6.0 接口子系统提供高达 64 GT/s 的数据速率,辅以满足高级异构计算架构需求的全面优化。

在子系统内,PCIe 控制器具有完整性和数据加密(IDE)引擎,专用于保护 PCIe 链路和通过它们传输的有价值数据。

PHY 方面,它还提供了对 CXL 3.0 的全面支持,支持高速缓存、一致性内存共享、以及扩展和池化的芯片级解决方案。

其它 PCI Express 特性:

兼容 PCIe 6.0(64 GT/s)、5.0(32 GT/s)、4.0(16 GT/s)、3.1/3.0(8 GT/s)和 PIPE 6.x(8 / 16 / 32 / 64 / 128-bit)

支持 SerDes 架构的 PIPE 10b/20b/40b/80b 位宽

支持 original PIPE 8b/16b/32b/64b/128b 位宽

符合 PCI-SIG 的 Single-Root I/O 虚拟化(SR-IOV)规范

支持 FLIT / 非 FLIT 模式下的多个虚拟通道(VC)

支持端点(Endpoint)、根端口(Root-Port)、双模(Dual-mode)、交换端口(Switch Port)配置

从 PCIe 6.0 向后支持到 PCIe 1.0 的速率

支持前向纠错(FEC)-- 低延迟的轻量级算法

支持 L0p 低功耗模式

最高 4-bit 数据路径奇偶校验保护

支持时钟门控和电源门控

RAS 功能 -- 包括 LTSSM 定时器覆盖、ACK/NAK/Replay/UpdateFC 定时器覆盖、未加扰的 PIPE 接口访问、Rx 和 Tx 路径上的错误注入、恢复详细状态等,允许在关键任务中安全可靠地部署 IP 系统芯片。

IDC 计算半导体研究副总裁 Shane Rau 表示:

PCI Express 在数据中心无处不在,而随着公司追求不断升级的速度和带宽、以迎合下一代应用程序的更高性能水平需求,CXL 的重要性也在日渐提升。

此外随着越来越多的芯片公司涌现、以支持新的数据中心架构,获得高性能接口的 IP 解决方案、也将是启用这一生态系统的关键。

最后,Rambus PCIe 6.0 接口子系统还具有如下主要特性:

支持 PCIe 6.0 规范,包括 64 GT/s 数据速率和 PAM4 信令。

通过部署低延迟前向纠错(FEC)以提升链路稳健性

支持高带宽效率的固定 FLIT 大小

向后兼容 PCIe 5.0、4.0 和 3.0/3.1