几年前,IBM 将其半导体制造业务出售给 GLOBALFOUNDRIES,但他们仍在奥尔巴尼纳米技术公司拥有价值数十亿美元的研究设施。IBM 在诸如 IEDM 之类的会议上非常活跃,而且这似乎有一个很好的光管地方,因为他们在这里公布的研究成果得到了很多媒体的关注。

在 2019 年的 Litho Workshop 上,我听到了来自IBM Albany 研究小组的演讲,他解释说 IBM 必须拥有研究线,因为他们需要最先进技术的处理器来支持他们的设备运行。我个人质疑这个观点,奥尔巴尼研究小组与三星合作,支持三星投产的 5nm 工艺。

笔者认为,三星的 5nm 工艺与台积电的 5nm 工艺相比,功耗、性能和密度都相对较差。我确信在支持 IBM 的过程中有特殊功能,但我也确信无需数十亿美元的研究投资也可以在台积电流程中实现相同的功能。我还认为有趣的是,他们说在开发过程中他们调高了 EUV 剂量(dose),直到获得良好的良率,然后他们将其转移给三星,期望三星减少 EUV 剂量。当三星开始加速他们的 5nm 工艺时,业界有传言称三星无法通过他们的 EUV 工具获得足够的晶圆(高 EUV 剂量导致低产量)并且产量很低。

IBM 每隔几年也会通过一些新的发展在主流媒体上引起轰动,但在我看来,很多发展并没有达到炒作的效果。例如,IBM 在 2021 年初宣布开发 2nm 技术,但正如我之前所写的那样,它更像台积电的 3nm 工艺而不是 2nm,与英特尔和台积电预期的 2nm 工艺相比,不太可能具有竞争力。

这并不是说 IBM 不做重要的研究,几年前他们负责包括铜金属化在内的许多关键行业创新,我只是质疑数十亿美元的半导体研究设施对于不生产半导体的公司是否有意义.

在本文中,我将讨论 IEDM 的三篇 IBM 论文。

第一篇,垂直传输纳米片技术,用于超越横向传输器件的 CMOS 缩放

在我看来,这篇论文是 IBM 典型的一个范例,我不希望他们辜负这个炒作。在这个论文中,作者指出,这项工作是与三星合作完成的。主流媒体已经发布了关于这个“突破”的消息,好像这将是一个生产解决方案。

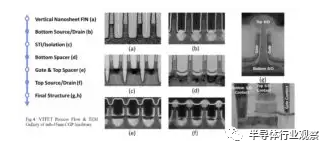

图 1 说明了垂直传输纳米片 (VTFET) 工艺。

这里的基本思想是不是在水平方向上制造纳米片,而是将它们变成垂直方向。在该论文中,垂直纳米片与 FinFET 进行了比较,并显示提供更好的性能和面积。我看到这有两个问题。

首先,我的理解是垂直晶体管非常适合 SRAM 的使用,其中互连需求简单且规则,但不适用于具有复杂互连需求的随机逻辑设计。Imec 之前展示了一些非常有趣的垂直 SRAM 工作,尽管它似乎没有在行业中获得任何关注。随着小芯片的出现,提供卓越密度的简单 SRAM 工艺非常有意义。但是再一次,对于逻辑用途,垂直晶体管面积可能会增加很多以适应互连要求。

我看到的第二个问题是将它与 FinFET 进行比较。从 FinFET 到堆叠水平纳米片 (horizontal nanosheets:HNS) 的转变已经在进行中。HNS 提供了优于 FinFET 的密度和性能优势,但更重要的是提供了长期的扩展路径。HNS 可以通过垂直堆叠更多片材来提高性能,它们还提供了引入介电壁(dielectric wall )的机会,创造了一种名为 Forksheets 的 Imec 创新,减少了 n 到 p 的间距。除此之外,在 3D-CMOS/CFET 架构中堆叠 n 和 p HNS 可提供更多的缩放比例,且水平 n 到 p 间距为零。除了 HNS,这些薄片还可以被 2D 材料替代,从而提供更大的缩放比例。驱动电流以及垂直鳍片的性能是由鳍片尺寸驱动的,我看不出这些设备如何像 HNS 那样扩展。

第二篇,下一代高性能计算纳米片技术的关键要素

在我看来,这篇论文比上一篇更有趣,因为它解决了所有主要前沿逻辑供应商都面临的 HNS 技术问题。IBM 过去在 HNS 方面做了很多出色的工作,本文以此为基础。

本文解决了两个 HNS 问题。

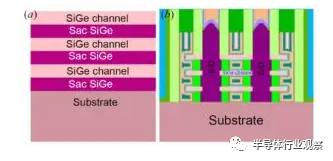

第一个问题是 HNS 的 pFET 迁移率很差。IBM 之前已经描述了两种提高 pFET 迁移率的技术,一种是在释放后修整沟道并沉积 SiGe 覆层。另一种技术是在应变松弛缓冲层(strain relaxed buffer layer)上制造沟道。

在本文中,SiGe 通道是通过在沉积原始纳米片堆叠时在较高 Ge 含量牺牲层上沉积较低 Ge 含量通道而形成的。Ge 含量的差异是为了启用选择性释放蚀刻,蚀刻掉牺牲膜并保持通道完好无损。SiGe 通道提供了改进的迁移率、改进的性能和更高的可靠性。

图 2 说明了 SiGe 通道 HNS pFET。

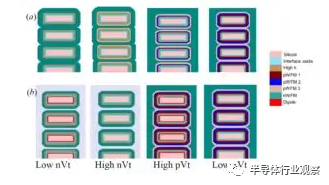

这里解决的第二个问题是如何为 HNS 实现多个均匀的阈值电压 (Vts)。对于 FinFET,鳍到鳍的距离相对较宽,并且可以通过沉积和选择性去除多种功函数金属来实现多个 Vts。使用 HNS,片到片 (Tsus) 的间距非常小,以至于没有足够的空间容纳一整堆功函数金属。金属也往往在 NS 外侧更厚,在纳米片之间更薄,导致 Vts 不均匀。

IBM 在十多年前率先使用偶极子(dipoles)来控制 VT,该技术现在正受到 HNS 的广泛关注,因为偶极子可以通过掺杂高 k 电介质来产生,并且不需要像多功函数金属那样需要额外的厚度. 偶极子还可以解决 Vt 非均匀性问题。

图 3 说明了功函数金属如何导致 Vts 不均匀以及无体积偶极子如何解决该问题。

用于高级逻辑技术的基于堆叠式全方位纳米片架构的后栅极 I/O 晶体管

我想讨论的第三篇论文是另一篇研究 HNS 问题的论文。

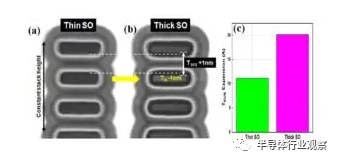

HNS 实施的另一个挑战是如何创建可以在更高电压下工作的 I/O 晶体管。在本文中,后栅极工艺流程结合了沉积氧化物和新型选择性氧化,产生了两种不同的栅极氧化物厚度。选择性氧化产生厚和薄的选择性氧化物,它们被添加到沉积的氧化物中。该技术的关键在于,生长的氧化物在氧化过程中会消耗硅,因此较厚的生长氧化物比生长的薄氧化物消耗更多的硅,从而打开片间间距 (Tsus) 以容纳较厚的氧化物。

图 4 显示了厚和薄栅氧化层 HNS 器件以及改进的 Tsus 以适应厚氧化层。

尽管媒体大肆宣传 IBM 在 IEDM 上发布的 Vertical-Transport Nanosheet,但我们认为 IBM 完善 HNS 流程的工作更有可能对行业产生影响。pFET 沟道迁移率、体积更小的 Vt 解决方案和高压 I/O 解决方案解决了业界目前正在努力解决的从 FinFET 到 HNS 过渡的问题。